因為直接連圖不好意思,所以說明一下大概的原理:

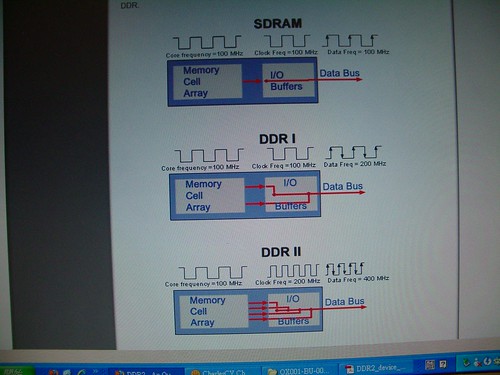

假設 RAM Cell clock 都是 100MHz...

- SDRAM 的 data 輸出和 data clock 的 rising edge 同步,所以也是 100MHz,因為一次一筆,所以不用 buffer 就直接輸出。

- DDR 的 data 輸出和 data clock 的 rising edge, falling edge 都同步,所以一樣用 100MHz,但是因為一個edge 只能 output 一筆,所以內部要先 buffer 一份

- DDR II 把輸出clock 增加一倍,而且也是 rising/falling edge 都輸出,所以內部要 buffer 3 份 data

本來以為內部buffer 的 data 用來解釋 CL (data - to CMD delay) ,但是好像不是喔。

內部 buffer 只需要 delay 待會 才要的 data,第一筆 data 還是可以直接 output 出去,不需要 delay 的喔。

沒有留言:

張貼留言